|

|

|

| |

| |

|

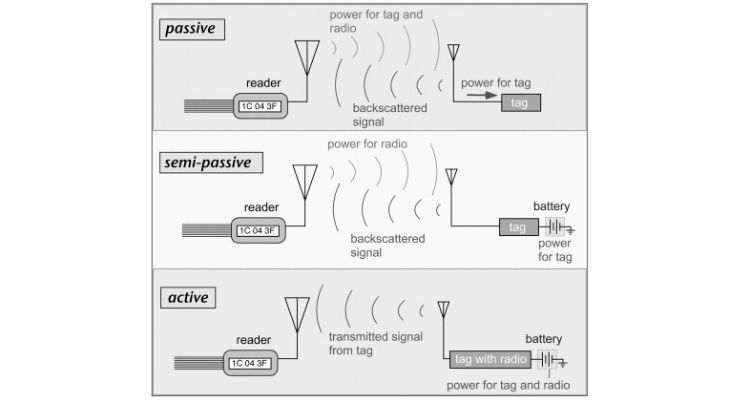

| What are the different taxonomies of RFID tags, and how do they differ? |

| The common way of categorizing RFID tags is based on how they utilize power for communication between the reader and the tag. They can also be classified based on operating frequency and absence/presence of chips. This first part of the FAQ will cover the passive, semi-passive, and active RFID tags categorized based on power. |

| Read more » |

|

| What is a PLL for analog signals? |

| A phase-locked loop (PLL) for analog signals generates an output with a phase that’s precisely matched to the phase of an input reference. This article begins by looking at how PLLs for analog signals operate, briefly compares them with digital PLLs and other PLL architectures, and closes by reviewing PLL application considerations. |

| Read more » |

|

|

| |

|

|

|

|

| |

| |

|

| Streamline Your Analog Design |

| Learn how Ansys offers the broadest suite of multiphysics solvers to give you accurate visibility into your advanced analog and mixed-signal designs. Improve the speed, ease, and rigor of your design and analysis with integrated simulation workflows. |

| Learn More » |

|

|

| |

|

|

|

|

| |

| |

|

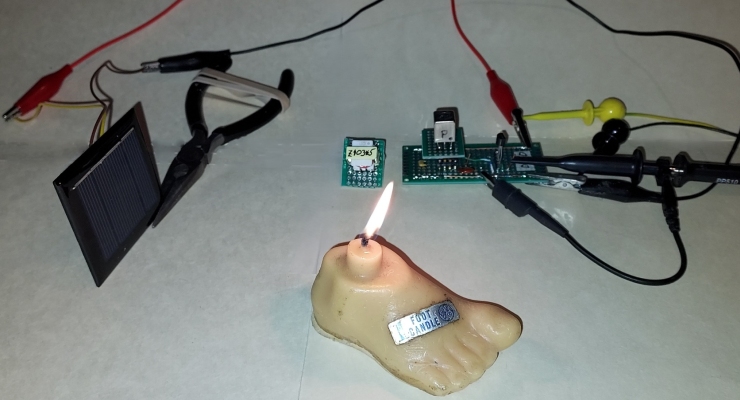

| Design a circuit for ultra-low power sensor applications |

| Sensors monitoring mechanical and biological systems must often scavenge power from the thing being sensed. The oscillator circuits shown here let you operate those sensors. Sensor circuits that connect to thermocouples, electromagnetic mechanical-to-electrical transducers, and piezoelectric... |

| Read more » |

|

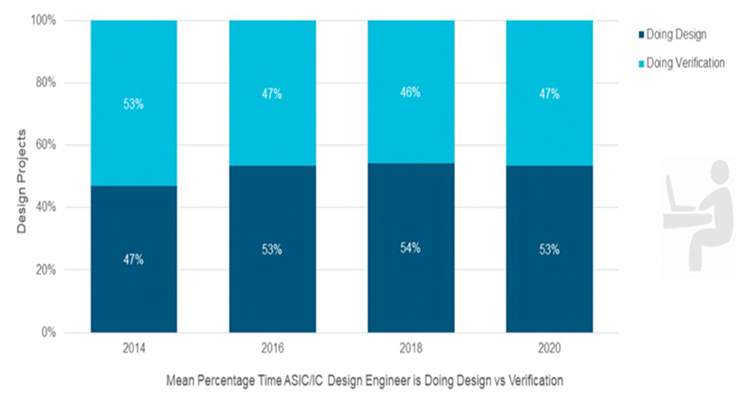

| How AI and ML optimize functional verification for EDA |

| Functional verification ensures that the register transfer layer (RTL) implementation of semiconductor designs operates according to specified requirements. Electronic engineers typically perform functional verification using hardware verification languages (HVLs) such as SystemVerilog paired with the universal verification methodology (UVM). |

| Read more » |

|

|

| |

|

|

|

|

|

|

|

|

|

|

|